启闳半导体科技(江苏)有限公司

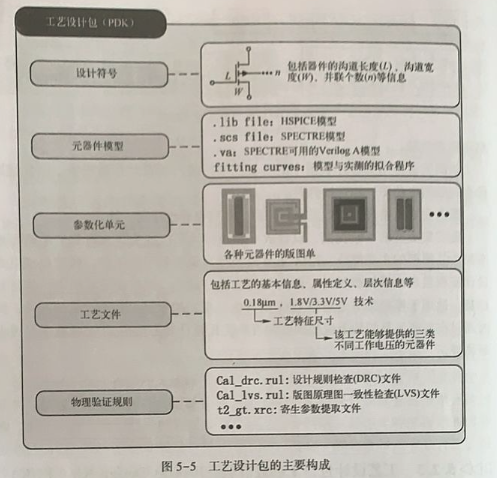

启闳半导体科技(江苏)有限公司工艺设计包(Process Design Kit, PDK)是一套用于集成电路设计、 描述工艺制造相关信息的数据文件,涵盖工艺支持的器件信息、工艺信息、物理规则信息等,是工艺和设计之间的桥梁。工艺设计包最早由Cadence 提出,并在其仿真电路设计平台Virtuoso 中基于SKILL语言实现,它通常包括设计符号、元器件模型、参数化单元、工艺文件及物理验证规则文件等内容,如图5-5所示。

设计符号是器件的电路图符号,通常涵盖器件的端口信息,如MOSFET的源极、漏极、栅极,以及影响器件性能的主要参数,如沟道长度与宽度、叉指(Fingers)个数等。

元器件模型是基于数学方程、等效电路和工艺数据拟合等方法描述元器件(如MOSFET、三极管及无源元件)的电压-电流关系,为芯片设计者提供的仿真模型文件,是晶体管级仿真验证的基础。为满足不同仿真工具的需要,工艺设计包中通常包含HSPICE模型及SPECTRE模型等;同时,为准确预估芯片性能参数的分布,元器件模型涵盖了工艺角( Process Corner)分析模型及蒙特卡洛(Monte Carlo)分析模型。

参数化单元( Parameterized Cell, PCell)是工艺设计包中的核心,基于SKILL语言编写,是满足版图设计规则检查及版图电路图一致性检查的参数化版图文件。参数化单元避免了重复创建单元版图,简化了单元版图的维护,使得设计人员的版图设计变得方便快捷。例如,设计者调用CMOS参数化单元,仅需通过修改属性参数便可得到不同尺寸的元器件版图。

工艺文件(Technology File)是用于版图设计和验证的工艺说明文件,它包含该工艺的特征尺寸,器件种类、GDS 设计数据层和工艺层的映射关系、设计数据层的属性定义、设计规则、电气规则、显示色彩定义、自动布局布线规则和图形格式定义等。

物理验证规则(Physical Vrifcaion Rules)文件包含了版图设计工艺规则检查文件(DRC 文件)、版图电路图一致性检查文件(LVS 文件)和版图寄生参数提取文件(XRC文件)等。